1.jpg)

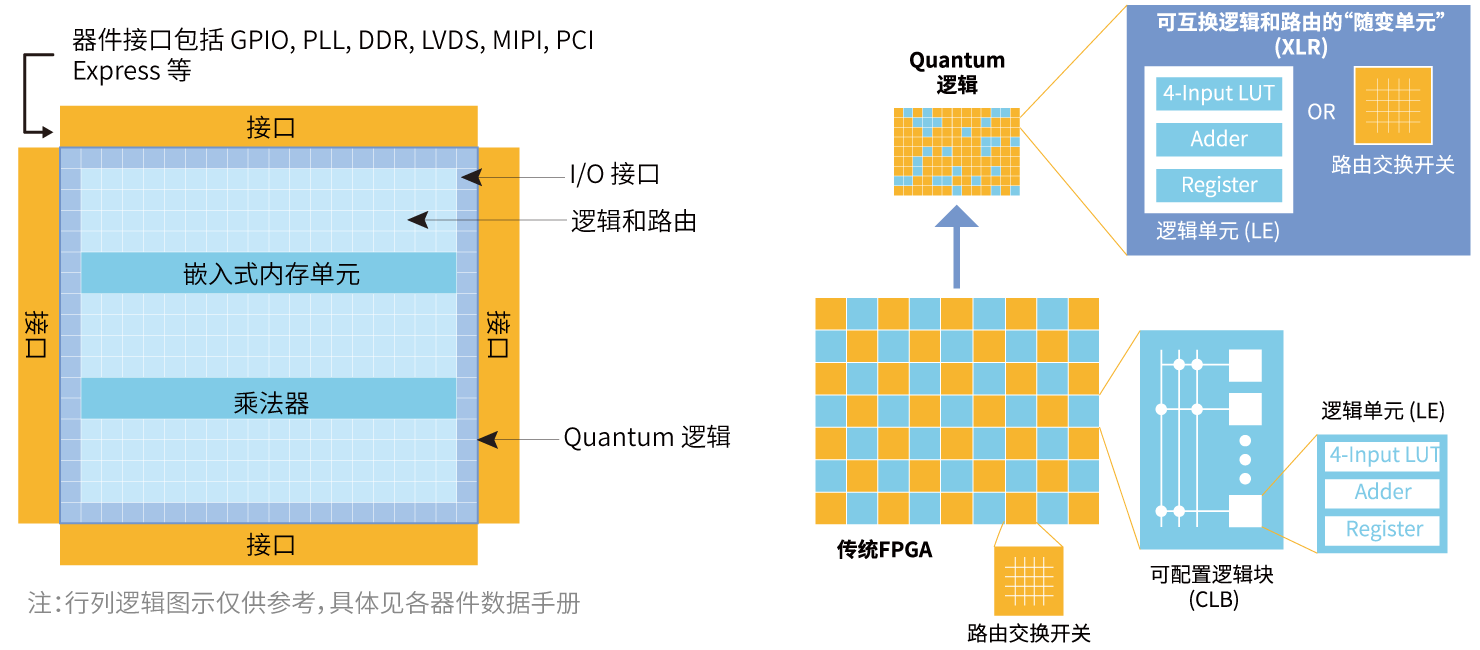

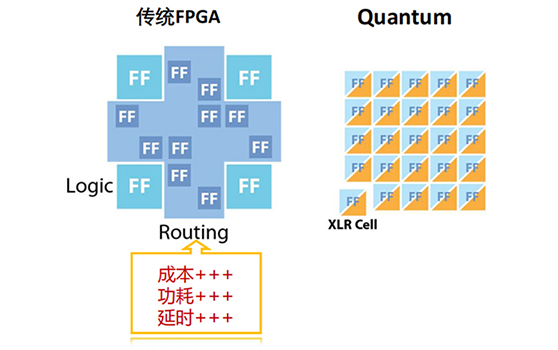

Based on Quantum™ technology, the Trion® family of products offers signigicant cost and size advantages over traditional FPGAs with logic and routing interchangeability, smaller silicon area and lower power consumption with the same resoutces.

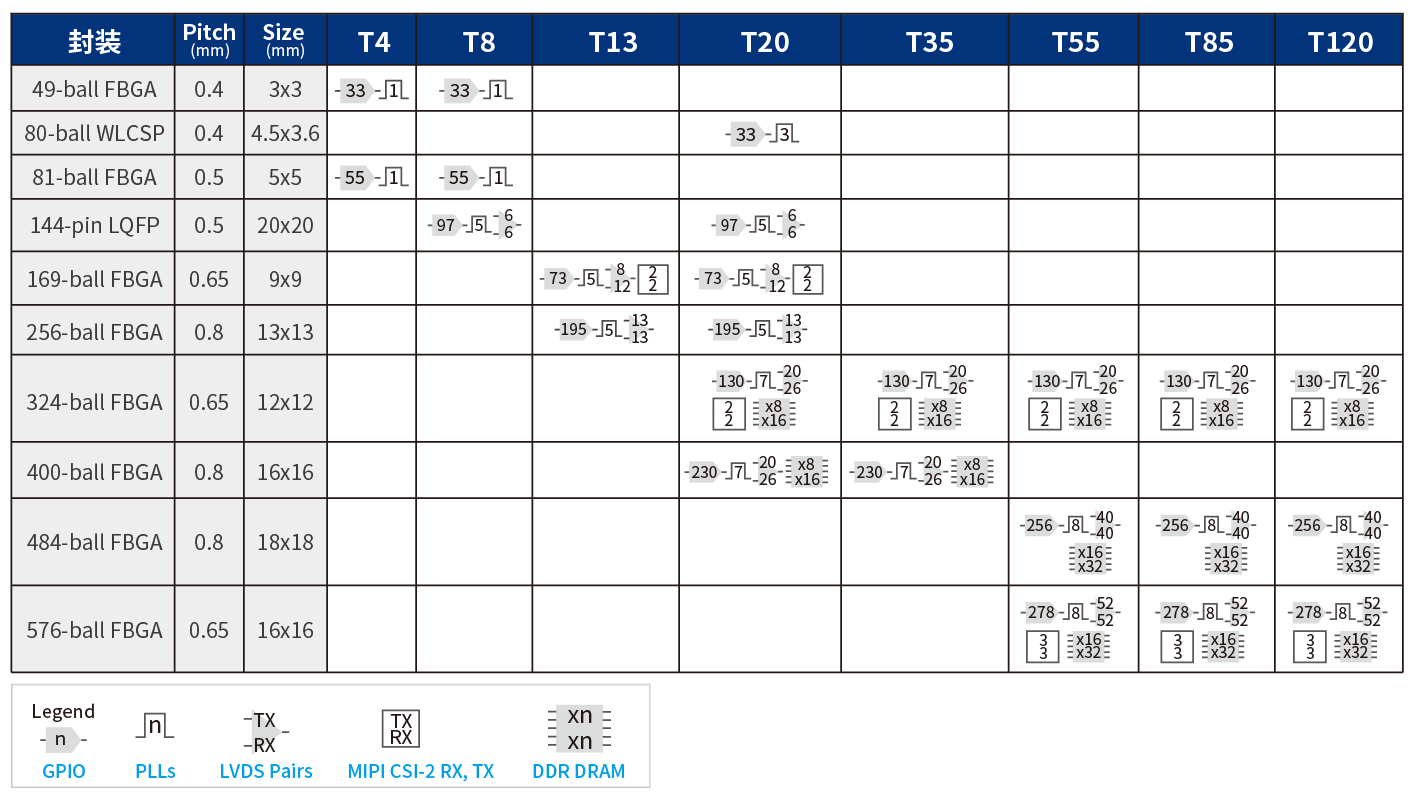

Trion FPGAs are based on SMIC's 40nm process, with logic densities from 4K to 120K logic cells (LE), embedded RAM modules and DSP modules, PLLs, and standard interfaces such as CPIO, MIPI, DDR, and LVDS.

The Trion family is suitable for many application areas such as video processing, industrial control, medical treatment, mobile, IoT, consumer electronics, and the rapidly growing machine vision, compute acceleration, edge computing and deep learning.

MIP: 4-lane MIPI D-PHY with built-in hard-core CSI-2 controller and up to 6Gbps bandwidth per MIPI D-PHY. It has advantages of low power consumption and low cost

LVDS: Support up to 800 Mbps

DDR: hard-core Memory controller supporting DDR3, LPDDR3, LPDDR2 devices, easy to use, with 1066 Mbps channel rate and up to 34Gbps or higher bandwidth

Up to 4X "Power-Performance-Area" (PPA) optimization

7 metal layers vs. 12+ metal layers

Unique design architecture easily scales to million-plus logic element (LE) densities

Ultra-easy silicon process portability

Based on the Elitestek mask programming process, users can program the chip once without using external configuration Flash.

This process offers unique advantages in application areas such as low cost and high security.

MPMs can only be programmed once by the Elitestek factory, and users need to pay Non-Recurring Engineering (NRE) fees in advance. Please contact Elitestek if you need it.

|

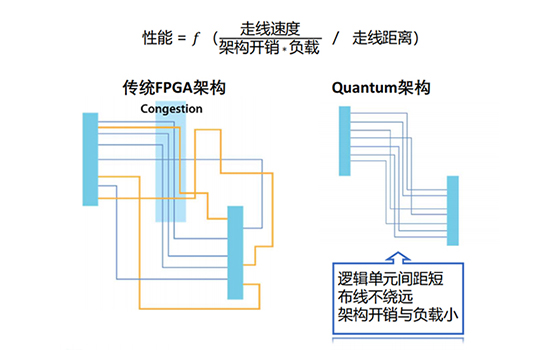

Alignment speed advantage

|

Alignment distance advantage

|

|

|

Low Logic Density

|

Conventional Architecture

|

Quantum

|

|

High Logical Density

|

Almost on a par

|

Quantum

|

.png)

(1).jpg)