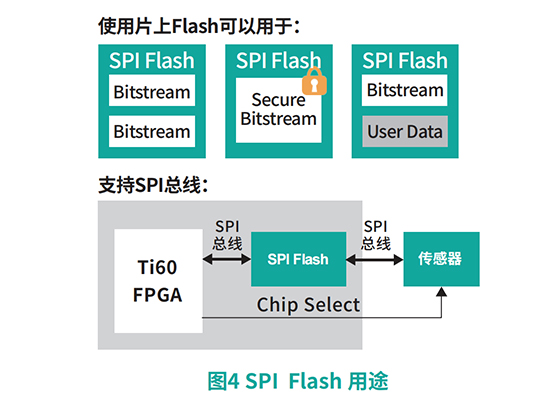

FPGAs typically require a separate device to store configuration (bitstream) files. The F100 package has a 16Mbit SPI Flash, so you don't have to make room on the board for a configuration chip. The Ti60 is clocked at up to 85MHz to keep the chip in a wake-up state and ready to run fast.

In addition, the internal Flash can do more than just save bitstreams. The Efifinity software supports bitstream compression for Titanium FPGAs, and the compressed Ti60 bitstream file uses only about half of the Flash space. You can use the rest to store non-volatile user data, a second bitstream file, or even a RISC-V application. In addition, if security is a concern in your design, we can support the generation of bitstream files that are protected by authentication, encryption, or both.

The SPI pins of the Flash are tied to the F100 package pins. This design allows you to use the Ti60 FPGA as an SPI master device connected to additional slave devices (on-board Flash and SPI-enabled external devices). For example, you can use the SPI bus to collect data from SPI sensors for processing.

1.jpg)